Titre: Logique séquentielle | Techniques d’intégration

Auteurs: Catherine Douillard, Gérald Ouvradou, Michel Jézéquel

Ecole: Ecole Nationale Supérieure des Télécommunications de Bretagne

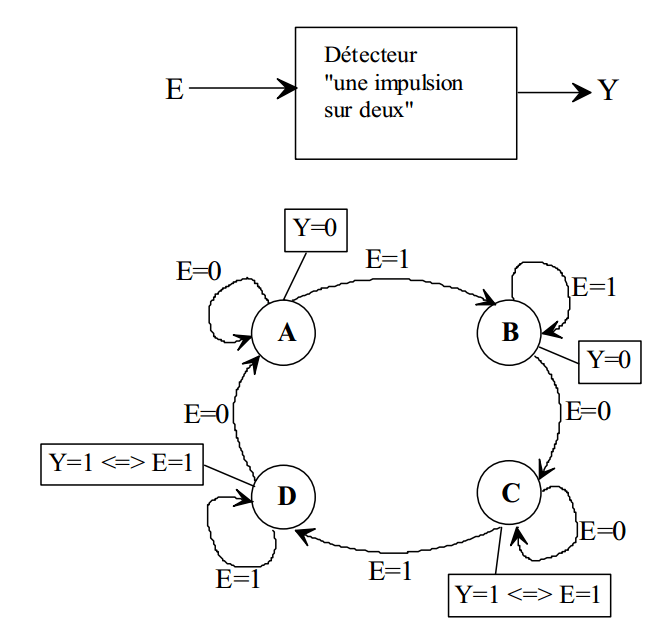

Résumé: Avec les circuits séquentiels, nous abordons un type nouveau de comportement par rapport à celui des circuits combinatoires, dans lequel la dimension temporelle joue un rôle fondamental. Pour le mettre en évidence, étudions un exemple simple de circuit séquentiel. Le circuit considéré dispose d’une entrée E(t) et d’une sortie Y(t), t étant la variable temps. Sa fonction consiste à reproduire sur sa sortie la seconde impulsion dans un train de deux impulsions consécutives présenté sur son entrée. Ce comportement est illustré par le chronogramme de la figure 5.1. On néglige, pour simplifier, le temps de propagation du circuit.

Extrait du sommaire:

Chapitre 5 : Fonctions de base de la logique séquentielle 1

1 INTRODUCTION1

2 MODELISATION D’UN SYSTEME SEQUENTIEL1

21 MODELE COMPORTEMENTAL : AUTOMATE A ETATS FINIS (AEF)1

22 MODELE STRUCTUREL : MACHINE DE MEALY3

23 UN EXEMPLE DE MISE EN OEUVRE D’UN AEF PAR UNE MACHINE DE MEALY4

24 SYSTEMES SEQUENTIELS SYNCHRONES (VERSUS ASYNCHRONES) 6

3 LE POINT MEMOIRE: DE LA BASCULE ASYNCHRONE A LA SYNCHRONISATION SUR FRONT

D’HORLOGE7

31 LE POINT MEMOIRE ELEMENTAIRE 7

32 LA BASCULE RS8

321 Structure de la bascule RS8

322 Analyse temporelle du comportement de la bascule RS-NOR9

323 Analyse statique de la bascule RS-NOR 10

34 LA BASCULE D A VERROUILLAGE OU D LATCH 11

331 Fonctionnalité de la D latch 11

332 Structure de la bascule D latch 12

333 Analyse temporelle du comportement de la D latch 14

3331 Temps de propagation 14

3332 Contraintes sur les entrées 15

34 LA BASCULE D A DECLENCHEMENT SUR FRONT OU D FLIP-FLOP 15

341 Introduction 15

342 Principe de fonctionnement de la bascule D à déclenchement sur front 16

343 Structure et analyse du comportement de la bascule D flip-flop 17

344 Analyse temporelle du comportement de la D flip-flop 18

3441 Temps de propagation 19

3442 Contraintes sur les entrées 19

35 LA BASCULE JK A DECLENCHEMENT SUR FRONT 19

36 COHABITATION DE FONCT IONS ASYNCHRONES ET SYNCHRONES 20

361 Initialisation des circuits séquentiels 20

362 Entrées statiques et dynamiques d’un circuit séquentiel synchrone 22

37 MODELE STRUCTUREL D’UN SYSTEME SEQUENTIEL SYNCHRONE 22

4 LES REGISTRES23

41 INTRODUCTION 23

42 LES REGISTRES DE MEMORISATION OU REGISTRES TAMPONS 23

43 LES REGISTRES A DECALAGE 24

431 Fonction décalage à droite 24

432 Fonction décalage à gauche 24

433 Chargement parallèle 25

434 Initialisation 25

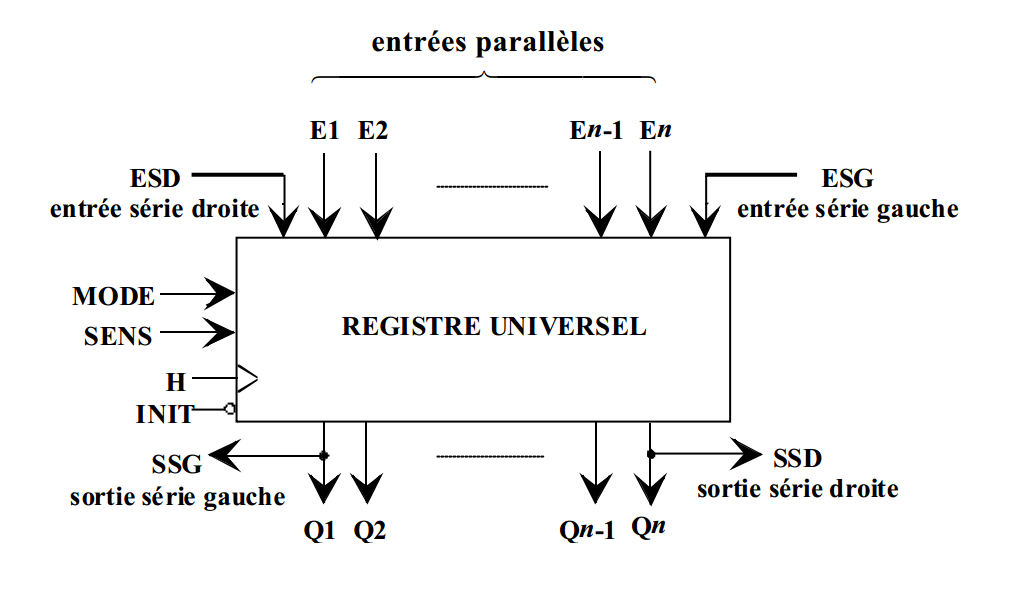

435 Registres universels 26

4351 Structure d’une cellule 27

4352 Identification avec le modèle de Mealy 27

436 Applications des registres à décalage 28

4361 Conversions parallèle-série et série-parallèle d’un train d’information 28

4362 Ligne à retard numérique 28

4363 Multiplication et division par 2n 28

4364 Réalisation de générateurs de séquences pseudo-aléatoires 29

5 LES COMPTEURS31

51 INTRODUCTION 31

511 La fonction de comptage 31

512 Le diviseur par 2 31

513 Comptage synchrone / asynchrone 32

52 LES COMPTEURS ASYNCHRONES 32

521 Compteurs binaires asynchrones à cycles complets 32

522 Décompteurs binaires asynchrones à cycles complets 33

523 Compteurs / décompteurs asynchrones à cycles incomplets 34

524 Conclusion sur l’utilisation des compteurs asynchrones 35

53 LES COMPTEURS SYNCHRONES 35

531 Méthode de synthèse des compteurs synchrones 35

5311 Exemple de synthèse de compteur binaire synchrone à cycle complet : compteur modulo 8 36

5312 Exemple de synthèse de compteur binaire synchrone à cycle incomplet : compteur modulo 5 38

5313 Exemple de synthèse de décompteur 39

5314 Initialisation d’un compteur synchrone 40

532 Les compteurs programmables 40

54 APPLICATIONS DES COMPTEURS 42

6 PARAMETRES DYNAMIQUES ET REGLES D’ASSEMBLAGE DES OPERATEURS SEQUENTIELS43

61 CHEMIN CRITIQUE ET FREQUENCE MAXIMALE DE FONCTIONNEMENT D’UN CIRCUIT SYNCHRONE 43

611 Définition 43

612 Exemples de calcul de la fréquence maximale de fonctionnement d’un circuit séquentiel 44

6121 Registre à décalage 44

6122 Compteur modulo 8 44

62 REGLES D’ASSEMBLAGE SEQUENTIEL ET ALEAS DE FONCTIONNEMENT 45

621 Initialisation 45

622 Horloge 45

6221 Décalage d’horloge 45

6222 Intégrité du signal d’horloge 46

623 Entrées statiques / entrées dynamiques 46

7 LES MEMOIRES A SEMI-CONDUCTEUR 49

71 INTRODUCTION 49

72 LES MEMOIRES A ACCES ALEATOIRE 50

721 Structure 50

722 Les mémoires vives ou RAM 51

7221 Les RAM statiques 52

7222 Les RAM dynamiques 54

7223 Critères de choix SRAM / DRAM 55

723 Les mémoires mortes ou ROM 56

7231 Les mémoires ROM et ROM programmables (PROM) 56

7232 Les mémoires reprogrammables REPROM 57

73 LES MEMOIRES A ACCES SEQUENTIEL 58

8 BIBLIOGRAPHIE59

Chapitre 6 : Fonctions et systèmes séquentiels complexes 61

1 INTRODUCTION61

11 DEFINITIONS 61

12 SOLUTIONS ARCHITECTURALES ETUDIEES POUR LA REALISATION D’UNE UNITE DE CONTROLE 62

2 LES MACHINES A ETATS FINIS62

21 SYSTEMES SYNCHRONES VERSUS ASYNCHRONES 62

22 MACHINE DE MEALY VERSUS MACHINE DE MOORE 63

23 MISE EN OEUVRE DES AUTOMATES 65

24 COMPLEXITE DES MACHINES A ETATS FINIS 66

3 LES SEQUENCEURS67

31 LE SEQUENCEUR CABLE 67

32 L’APPROCHE MICROPROGRAMMEE 68

4 BILAN COMPARATIF71

5 METHODES DE CONCEPTION D’UNE UNITE DE CONTROLE73

51 DEMARCHE ASSOCIEE A LA CONCEPTION D’UNE MACHINE A ETATS FINIS 73

511 Synthèse d’une machine de Mealy : la méthode d’Huffman 73

5111 Méthode manuelle 73

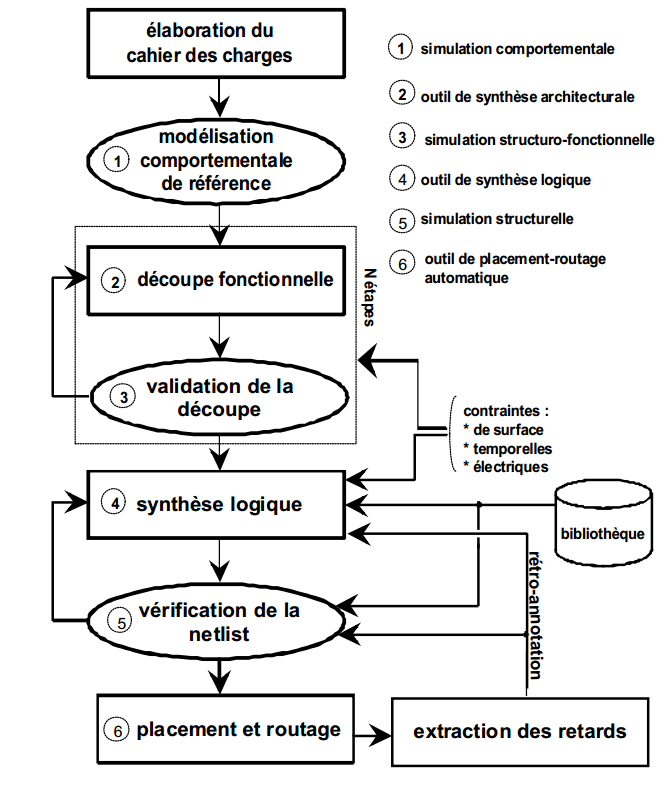

5112 Méthode utilisant des outils de synthèse logique automatique et de simulation 74

52 DEMARCHE ASSOCIEE A LA CONCEPTION DES SEQUENCEURS 74

521 Partie commune aux séquenceurs câblés et microprogrammés 74

522 De l’automate à états finis vers la machine de Von Neumann 74

523 Séquenceur câblé 76

523 Séquenceur microprogrammé 77

53 ILLUSTRATION AVEC LE CONTROLEUR D’ALTERNAT POUR LIAISONS SYNCHRONES 77

531 Spécification de l’application 78

532 Découpage fonctionnel du contrôleur d’alternat 79

533 Illustration de la méthode de Huffman : réalisation de l’automate de la fonction de détection de fanion81

5331 Spécification comportementale de l’automate 81

5332 Codage des états de l’automate 82

5333 Établissement de la table de transition de l’automate 82

5331 Réalisation de la machine à l’aide de composants élémentaires (portes et bascules D) 82

534Illustration de la méthode de synthèse d’un séquenceur : réalisation de l’automate d’émission 84

5341 Cahier des charges de l’automate d’émission 84

5342 Spécification comportementale de l’automate 84

5343 Reformalisation du graphe en algorithme 85

5344 Cas du séquenceur câblé 85

5345 Cas du séquenceur microprogrammé 87

6 BIBLIOGRAPHIE91

Chapitre 7 : Techniques d’intégration de systèmes numériques93

1 INTRODUCTION93

2 LES CIRCUITS93

21 LA FABRICATION DES CIRCUITS INTEGRES 93

211 La microlithographie 94

212 Fabrication d’un circuit intégré CMOS 94

22 LES CIRCUITS STANDARD 97

221 Les fonctions simples 98

222 Les fonctions complexes 98

2221 Processeurs dédiés 98

2222 Processeurs d’usage général 98

2223 Processeurs spécialisés 98

223 Mémoires 98

23 LES CIRCUITS SPECIFIQUES A L’APPLICATION (ASIC) 99

231 Les ciselés (Full Custom) 99

232 Les précaractérisés (Standard Cell) 99

233 Les prédiffusés (Gate Array) 99

234 Les composites 100

24 LES CIRCUITS PROGRAMMABLES 100

241 Les PLD (Programmable Logic Device) 100

242 Les FPGA (Field Programmable Gate Array) 101

243 L’évolution des circuits 102

25 LES CRITERES DE CHOIX 103

3 LES OUTILS DE CONCEPTION104

4 BIBLIOGRAPHIE106

Télécharger le fichier PDF: Logique séquentielle