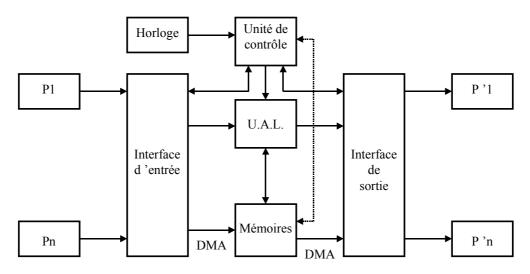

# ARCHITECTURE D'UNE MACHINE INFORMATIQUE SYNCHRONE PILOTEE PAR UNE HORLOGE

# I) <u>Fonctions de base d'une machine informatique</u>

- ➤ Contenir de façon permanente les tâches à exécuter (mémoire programme) en ROM ou sur support magnétique.

- Contenir de façon temporaire des données (mémoire de travail) en RAM.

- Permettre un dialogue avec l'extérieur (circuit d'interface entrée/sortie) :

- ♥ PIA- ACIA- TIMER

- ♥ PIO- USART

- ♥ SIO- UART.

- > Effectuer des opérations arithmétiques et logiques élémentaires (UAL, en anglais ALU).

- ➤ Organiser des transits d'informations (unité de contrôle : U.C.)

- ➤ Cadencer les différentes informations (Horloge)

- ➤ Pointer l'étape du programme en cours (P.C. : compteur programme, en anglais Program Counter).

# II) Schéma fonctionnel d'une machine informatique

## A) Pn: Périphériques d'entrées

- ➤ Clavier

- ➤ Souris

- ➤ Joystick

- ➤ Ecran tactile

- ➤ Lecteur de bande magnétique

- > Lecteur de cartes

- ➤ Chaînes d'acquisition de données

- > Crayon optique

#### B) Registres mémoires

A accès dit aléatoire c'est à dire, temps d'accès indépendant de l'emplacement de la donnée stockée.

➤ Lecture seule : ROM ➤ RAM : Statique PROM Dynamique

REPROM

### C) Mémoires de masse

Accès séquentiel : Bandes magnétiques

➤ Accès aléatoire : Disquettes

Disques durs Cédéroms

## D) P'n: Périphériques de sortie

➤ Dispositifs de visualisation : DELs

Affichage alphanumérique

Ecran vidéo

- ➤ Imprimante

- ➤ Table traçante

- > Perforatrice de bandes

- > Synthétiseur vocal

- ➤ Lecteur disquette

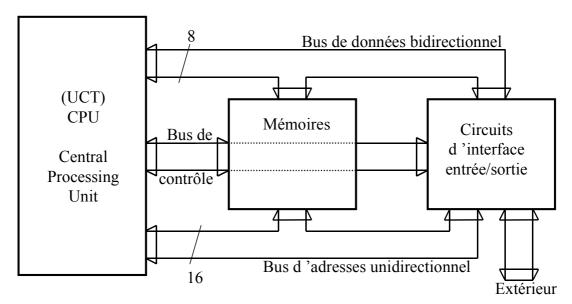

# III) Architecture d'un système à microprocesseur

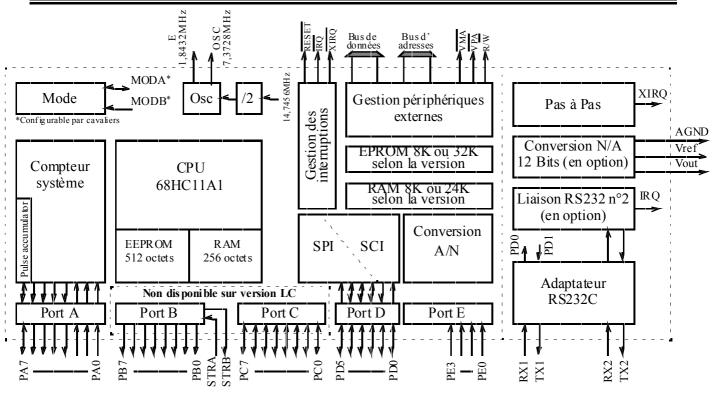

## A) Structure: µP 68HC11 MOTOROLA

Les périphériques chez MOTOROLA sont considérés comme des accès mémoires.

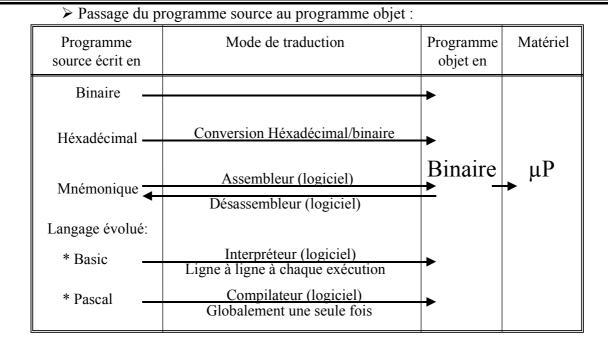

#### B) Notion de programme source et programme objet

➤ Programme source : Traduction de l'algorithme dans un langage compréhensible par la machine informatique (BASIC, PASCAL, C, FORTRAN, COBOL, ALGOL, PL1, ADA, LOGO, LSE, DELPHI, etc ...).

➤ Programme objet : Traduction du programme source en instructions codées en binaire, seul langage exécutable par le microprocesseur.

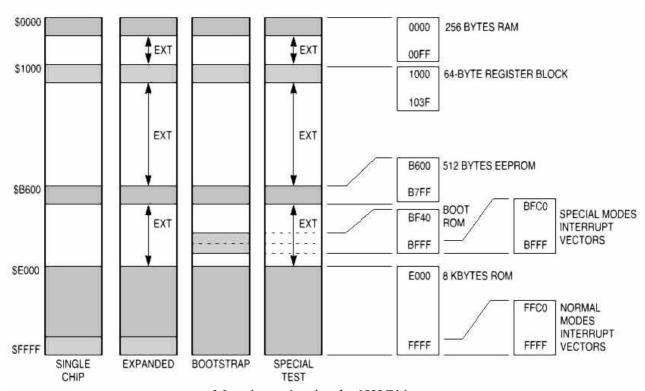

## C) Structure interne 68HC11

Mapping mémoire du 68HC11.

Le 68HC11 est un microcontrôleur. C'est un microprocesseur qui possède de la RAM, ROM et divers périphériques d'entrées/sorties. Un microcontrôleur peut donc être utilisé seul, car il est à lui seul une machine informatique. Un microprocesseur, PENTIUM, 6809, Z80, etc..., ne peut fonctionner seul, il a nécessairement besoin de ROM et de RAM externes.

Architecture d'un microprocesseur de la famille 68HC11.

L'unité centrale 68HC11 est dérivée du « vieux » 6801. Il existe une grande variété de 68HC11, issus du 68HC11A8.

Autour de l'unité centrale du 68HC11, on trouve de la mémoire. Elle se subdivise au maximum en trois blocks distincts dont la taille et la présence varient selon les références exactes du circuit : RAM ( 256 octets minimum), ROM (présente ou absente) et EEPROM.

Cette unité centrale est entourée d'un certain nombre de ports parallèles baptisés port A à port E qui peuvent être bidirectionnels ou unidirectionnels selon le cas.

Un timer est également disponible. Il comporte plusieurs timers très évolués, ainsi qu'un accumulateur d'impulsions, une horloge temps réel et un chien de garde (ou COP : Computer Operating Properly) destiné à surveiller le fonctionnement du microcontrôleur.

Un convertisseur analogique/numérique à huit entrées complète les ressources internes du 68HC11.

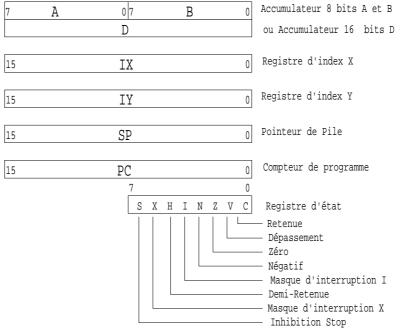

## D) Accumulateurs

Registres de travail du 68HC11

#### > Accumulateurs A, B et D:

Les registres A et B sont des accumulateurs 8 bits indépendants utilisés pour toutes opérations arithmétiques et logiques. A et B peuvent être concaténés et former un accumulateur D de 16 bits. Attention cet accumulateur n'est pas indépendant de A et B.

## Registres d'index X et Y :

Les registres d'index X et Y, indépendants, possèdent 16 bits chacun, puisque la capacité d'adressage du 68HC11 est de 16 bits d'adresses. Leur rôle premier est d'être utilisé pour l'adressage indexé, mais ils peuvent être utilisés pour le stockage temporaire de données, ou pour quelques opérations arithmétiques élémentaires.

#### > Pointeur de pile S :

Le pointeur de pile S est un registre 16 bits. Ce registre pointe sur la première adresse libre de la zone mémoire définie pour ranger différents paramètres, tel registre PC, registre CCR, etc ..., suivant la demande (interruption, appel à un sous-programme). Il est indispensable de l'initialiser à une adresse RAM, sinon à la première interruption ou appel à un sous-programme, le programme se plantera (bug).

#### > Compteur programme ou PC :

Le compteur programme, PC, indique l'adresse du prochain code binaire à 8 bits (instruction ou valeur de travail) à traiter. La taille du registre PC est donc de 16 bits.

#### Registre d'état ou CCR :

Le registre d'état ou CCR ( Condition Code Register) est un registre sur 8 bits. Chaque bit à une signification particulière.

Le bit C (Carry): C est mis à 1 lorsqu'une opération arithmétique génère une retenue. Il est également utilisé comme indicateur d'erreur lors d'une multiplication ou d'une division, et sert lors de certaines opérations de décalage ou rotation qui peuvent passer par son intermédiaire ou non.

🖔 Le bit V (oVerflow) : V est mis à 1 lorsqu'une opération arithmétique génère un débordement de l'accumulateur.

\$\triangle\$ Le bit Z (Zero): Z est mis à 1 lorsque le résultat de l'instruction exécuté est nul.

Le bit N (Negative): N est **mis à 1** lorsque le **résultat** de la dernière opération arithmétique réalisée **est négatif** (bit de poids fort du résultat à 1).

Le bit H (Half carry): H, demi-retenue, est mis à 1 lors d'une retenue entre les bits 3 et 4 d'une opération arithmétique. Il n'est affecté que par les instructions ADD, ADC et ABA, et est ensuite exploité par l'instruction DAA pour réaliser de l'arithmétique DCB (en anglais BCD), c'est à dire codée en fait sur 2 groupes de 4 bits.

Le bit I (Interrupt mask): I interdit toute interruption masquable lorsqu'il est mis à 1. C'est à dire qu'il permet d'autoriser les interruptions du TIMER, ACIA et autres. Suite à un RESET, I est mis à 1.

Le bit X (Xirq interrupt mask): X interdit toute interruption masquable lorsqu'il est mis à 1. Suite à un RESET, X est mis à 1. Attention XIRQ est une interruption non masquable en général, mais dans le cas du 68HC11, il est possible de la masquer.

Le bit S (Stop disable): S est mis à 1 pour interdire l'exécution de l'instruction STOP. Elle sera considérée comme un simple NOP (No OPeration).

Il existe certaines instructions pour manipuler directement certains bits du registre CCR.

# E) <u>Définitions des signaux de contrôle</u>

♦ Alimentation (VDD et VSS): VSS=0V et VDD=+5V à 5%.

# $\$ MODA/ $\overline{LIR}$ et MODB/Vstby :

| MODB | MODA | Mode de fonctionnement |

|------|------|------------------------|

| 0    | 0    | Normal- Circuit seul   |

| 0    | 1    | Normal- Etendu         |

| 1    | 0    | Spécial- Bootstrap     |

| 1    | 1    | Spécial- Test          |

#### ♥ EXTAL et XTAL :

Entrées du quartz pour générer le signal d'horloge E. On peut aussi appliquer seulement un signal d'horloge sur l'entrée EXTAL.

#### & E:

E est une sortie d'horloge de bus. Sa fréquence est égale au quart de la valeur du quartz. L'état logique de E, haut ou bas, indique si des données ou des adresses valides sont présentes sur le bus du 68HC11.

#### ♥ RESET :

Entrée RESET active au niveau bas. Mais elle peut devenir une sortie, dans le cas du chien de garde ou COP, active là aussi au niveau bas.

# ♥ IRQ:

Entrée d'interruption masquable (voir bit I du registre CCR et bit IRQE du registre option).

#### ♥ XIRO:

Entrée d'interruption non masquable (voir bit X du registre CCR). Cette interruption est quand même masquable.

#### ♥ VREFL et VREFH:

VREFL et VREFH sont respectivement des entrées de référence basse et haute du convertisseur analogique/numérique. Pour une bonne précision, la différence de potentiel entre VREFH et VREFL doit être au moins de 2,5V, mais restée dans les limites de VDD et VSS.

#### Separate:

PE0 à PE7 sont des entrées du port parallèle E. Ces lignes sont unidirectionnelles et ne fonctionnent qu'en entrée. De plus elles sont partagées avec les entrées du convertisseur analogique/numérique. Il est possible de faire travailler le port E en numérique et en analogique en même temps (il faudra soigner le programme sous peine de légères perturbations).

#### Separate Port D:

PD0 à PD5 sont des entrées ou sorties du port parallèle D. Ces lignes sont programmables indépendamment en entrée ou sortie. La programmation du port D est réalisée par le registre DDRD, registre de programmation des lignes du port D.

#### Sport C:

PC0 à PC7 sont des entrées ou sorties du port parallèle C. Ces lignes sont programmables indépendamment en entrée ou sortie. La programmation du port C est réalisée par le registre DDRC, registre de programmation des lignes du port C.

En mode étendu, le port C devient bus de données (8 bits) ou bus de poids faible des adresses (8 bits) (multiplexage des différents bus).

#### ♥ Port B:

PB0 à PB7 sont des sorties du port parallèle B.

En mode étendu, le port B devient bus de poids fort des adresses (8 bits).

#### ♥ STRA/AS:

STRA est une entrée permettant de mémoriser des données présentent sur le port C en entrée. STRA est actif sur un front programmable.

### $\P$ STR B/R/ $\overline{W}$ :

STRB est une sortie indiquant lorsque des données sont présentent sur les lignes du port B et C qui ont été placées en sorties (fonction strobe).

#### Separate Port A:

PA0 à PA2 sont des entrées du port parallèle A, P3 à PA6 sont les sorties de ce port et PA7 est l'entrée ou sortie de ce même port.

Ces lignes sont partagées par le timer. PA0 à PA2 sont les entrées de capture IC3 à IC1 du timer. PA3 à PA6 sont les sorties de comparaison OC1 à OC5 du timer. PA7 peut être configuré en entrée de capture ou sortie de comparaison.

# IV) Structures algorithmiques fondamentales

#### A) Définitions :

➤ Organigramme : (en anglais flowchart, se dit aussi ordinogramme) c'est un schéma synoptique qui analyse dans le détail les différentes phases du problème à traiter.

Algorithgramme : C'est la transposition d'un organigramme en tâches simplifiées.

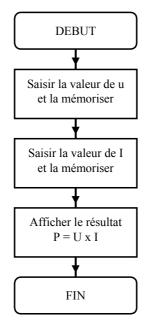

# B) Structure linéaire ou séquentielle :

#### Ex: $P = U \times I$

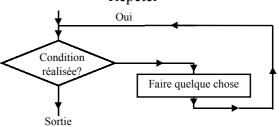

#### C) Structure itérative :

# 1) <u>Structure itérative : boucle « tant que » :</u>

Tant que < condition réalisée > Faire quelque chose Répéter

<u>Remarque</u>: Le travail peut ne jamais être effectué.

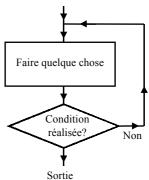

# 2) <u>Structure itérative : boucle « jusqu'à » :</u>

Faire quelque chose

Jusqu'à ce que < condition

réalisée >

<u>Remarque</u>: Le travail à effectuer l'est au moins une fois.

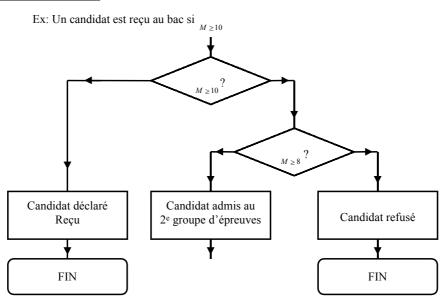

## D) Structure alternative:

# V) Modes d'adressage

## A) Adressage inhérent :

Ce mode n'est pas à proprement parler un mode d'adressage, mais tous les fabricants le décomptent comme tel.

Les instructions agissent sur les registres internes du microprocesseur. Les instructions comportent donc un code opérateur seul sans opérande.

ABA Additionne le contenu de A avec celui de B. Le résultat se trouve dans A. ASLA Effectue un décalage vers la gauche des bits de A.

# B) Adressage immédiat :

Dans ce mode d'adressage, le code opérateur est suivi par la donnée à manipuler, code opérande, qui est précédée par le symbole #. L'instruction est donc composé d'un code opérateur, d'un # et enfin d'un code opérande.

➤ LDAA #55 Stocke la valeur 55 en décimale dans le registre A. LDD #\$5A0 Stocke la valeur 5A0 en hexadécimale dans le registre D.

## C) Adressage direct:

Ce mode d'adressage, que l'on peut confondre avec l'adressage immédiat, est le premier « vrai » mode d'adressage du 68HC11. Le code opérateur est suivi d'un octet non signé qui est l'adresse effective de la donnée , ou opérande, à manipuler.

Ne codant l'adresse que sur un octet, il n'est possible que d'adresser les 256 premiers octets, l'adresse \$00 à l'adresse \$FF, de l'espace adressable du microcontrôleur.

LDAA \$55 Stocke la valeur contenue à l'adresse \$0055 dans le registre A.

ADDA 55 Additionne la valeur contenue à l'adresse \$0037 avec la valeur contenue dans le registre A. Résultat de l'opération arithmétique dans le registre A.

#### D) Adressage étendu ou absolu :

Ce mode d'adressage est une évolution du précédent et permet d'atteindre n'importe quelle adresse mémoire car il autorise un codage de l'adresse effective sur deux octets, ou 16 bits. Le champs mémoire adressable est donc de \$0000 à \$FFFF.

L'opérande est donc codé sur 2 octets.

LDAA \$B05A Stocke la valeur contenue à l'adresse \$B05A dans le registre A.

ADDA \$B05A Additionne la valeur se trouvant à l'adresse \$B05A avec la valeur contenue dans le registre A. Résultat de l'opération arithmétique dans le registre A.

## E) Adressage indexé avec déplacement d'une constante :

Ce mode d'adressage est particulièrement souple et fait intervenir deux facteurs dans le calcul de l'adresse effective : le contenu d'un des registres d'index X ou Y et une donnée appelée déplacement ou offset (non signé).

► LDAA \$33,X Stocke la valeur se trouvant à l'adresse X+\$33 dans le registre A.

ADDA \$33,Y Additionne la valeur contenue à l'adresse Y+\$33 avec la valeur contenue dans le registre A. Résultat de l'opération arithmétique dans le registre A.

STAB ,X Stocke la valeur contenue dans le registre B à l'adresse X, car l'offset est de 0 ici.

## F) Adressage indexé avec déplacement accumulateur :

Ce mode fonctionne de la même manière que précédemment, cependant l'offset n'est plus une constante, mais un registre du 68HC11.

➤ LDAA B,X Stocke la valeur se trouvant à l'adresse X+B dans le registre A. X étant un registre sur 16 bits et B un registre sur 8 bits.

<u>Remarque</u>: On peut conclure que l'offset est une donnée sur 8 bits non signée. Il ne peut donc varier que \$00 à \$FF.

## G) Adressage relatif:

Ce mode d'adressage se rencontre quasiment sur tous les microprocesseurs, mais n'est utilisé ici que pour les instructions de saut et branchement. Il spécifie l'adresse effective sous forme d'un déplacement qui est donc ajouté à la valeur courante du PC pour déterminer l'adresse de poursuite du programme. Comme lors de l'exécution d'une instruction, le PC pointe toujours sur l'instruction suivante, l'adresse effective est en fait égale à la valeur courante du PC+2+le déplacement.

Le déplacement est codé sur un octet signé, d'où un déplacement de -128 à +127 en base décimale.

> BEQ \$FB Après exécution de la ligne de commande le contenu du PC sera

additionné à -5 si le bit Z est à 1, sinon le contenu du PC

s'incrémentera de +2.

BCC \$10 Après exécution de la ligne de commande le contenu du PC sera

additionné à +16 si le bit C est à 0, sinon le contenu du PC s'incrémentera de +2.

# VI) Jeux d'instructions du 68HC11

#### Cycle

\* Infinity or until reset occurs

\*\* 12 Cycles are used beginning with the opcode fetch. A wait state is entered which remains in effect for an integer number of MPU E-Clc cycles (n) until an interrupt is recognized. Finally, two additional cycles are used to fetch the appropriate interrupt vector (14 + n total).

#### Operands

dd = 8-Bit Direct Address (\$0000 - \$00FF) (High Byte Assumed to be \$00)

ff = 8-Bit Positive Offset \$00 (0) to \$FF (255) (Is Added to Index)

hh = High-Order Byte of 16-Bit Extended Address

ii = One Byte of Immediate Data

jj = High-Order Byte of 16-Bit Immediate Data

kk = Low-Order Byte of 16-Bit Immediate Data

II = Low-Order Byte of 16-Bit Extended Address

mm = 8-Bit Mask (Set Bits to be Affected)

rr = Signed Relative Offset \$80 (-128) to \$7F (+127)

(Offset Relative to Address Following Machine Code Offset Byte))

#### Operators

( ) Contents of register shown inside parentheses

← Is transferred to↑ Is pulled from stack↓ Is pushed onto stack

Boolean AND

Arithmetic Addition Symbol except where used as Inclusive-OR symbol in Boolean Formula

⊕ Exclusive-OR

\* Multiply

: Concatenation

Arithmetic subtraction symbol or Negation symbol (Two's Complement)

#### Condition Codes

Bit not changed

Bit always cleared

Bit always set

$\Delta$  Bit cleared or set, depending on operation

$\downarrow$  Bit can be cleared, cannot become set

Table 3-2 Instruction Set (Sheet 1 of 6)

| Mnemonic            | Operation                   | Description                  | Addressing                                    | I                             | Condition Codes            |                       |   |   |   |   |   |   |   |   |

|---------------------|-----------------------------|------------------------------|-----------------------------------------------|-------------------------------|----------------------------|-----------------------|---|---|---|---|---|---|---|---|

|                     |                             |                              | Mode                                          | Opcode                        | Operand                    | Cycles                | S | Х | Н | 1 | N | Z | ٧ | С |

| ABA                 | Add<br>Accumulators         | A + B ⇒ A                    | INH                                           | 1B                            | _                          | 2                     | _ | _ | Δ | _ | Δ | Δ | Δ | Δ |

| ABX                 | Add B to X                  | IX + (00 : B) ⇒ IX           | INH                                           | 3A                            | _                          | 3                     | _ | _ | _ | _ | _ | - | _ | _ |

| ABY                 | Add B to Y                  | IY + (00 : B) ⇒ IY           | INH                                           | 18 3A                         | _                          | 4                     | _ | _ | _ | _ | _ | _ | _ | _ |

| ADCA (opr)          | Add with Carry<br>to A      | $A + M + C \Rightarrow A$    | A IMM A DIR A EXT A IND,X A IND,Y             | 89<br>99<br>B9<br>A9<br>18 A9 | ii<br>dd<br>hh II<br>ff    | 2<br>3<br>4<br>4<br>5 |   | _ | Δ | _ | Δ | Δ | Δ | Δ |

| ADCB (opr)          | Add with Carry<br>to B      | $B + M + C \Rightarrow B$    | B IMM B DIR B EXT B IND,X B IND,Y             | C9<br>D9<br>F9<br>E9<br>18 E9 | ii<br>dd<br>hh II<br>ff    | 2<br>3<br>4<br>4<br>5 | _ | _ | Δ | _ | Δ | Δ | Δ | Δ |

| ADDA (opr)          | Add Memory<br>to A          | $A + M \Rightarrow A$        | A IMM<br>A DIR<br>A EXT<br>A IND,X<br>A IND,Y | 8B<br>9B<br>BB<br>AB<br>18 AB | ii<br>dd<br>hh II<br>ff    | 2<br>3<br>4<br>4<br>5 | _ | _ | Δ | _ | Δ | Δ | Δ | Δ |

| ADDB (opr)          | Add Memory<br>to B          | B + M ⇒ B                    | B IMM B DIR B EXT B IND,X B IND,Y             | CB<br>DB<br>FB<br>EB<br>18 EB | ii<br>dd<br>hh II<br>ff    | 2<br>3<br>4<br>4<br>5 |   |   | Δ |   | Δ | Δ | Δ | Δ |

| ADDD (opr)          | Add 16-Bit to D             | D + (M : M + 1) ⇒ D          | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y           | C3<br>D3<br>F3<br>E3<br>18 E3 | jj kk<br>dd<br>hh II<br>ff | 4<br>5<br>6<br>6<br>7 | _ | _ | _ | _ | Δ | Δ | Δ | Δ |

| ANDA (opr)          | AND A with<br>Memory        | $A \cdot M \Rightarrow A$    | A IMM<br>A DIR<br>A EXT<br>A IND,X<br>A IND,Y | 84<br>94<br>B4<br>A4<br>18 A4 | ii<br>dd<br>hh II<br>ff    | 2<br>3<br>4<br>4<br>5 | _ | _ | _ | _ | Δ | Δ | 0 | _ |

| ANDB (opr)          | AND B with<br>Memory        | $B \bullet M \Rightarrow B$  | B IMM<br>B DIR<br>B EXT<br>B IND,X<br>B IND,Y | C4<br>D4<br>F4<br>E4<br>18 E4 | ii<br>dd<br>hh II<br>ff    | 2<br>3<br>4<br>4<br>5 | _ | _ | _ | _ | Δ | Δ | 0 | _ |

| ASL (opr)           | Arithmetic<br>Shift Left    |                              | EXT<br>IND,X<br>IND,Y                         | 78<br>68<br>18 68             | hh II<br>ff<br>ff          | 6<br>6<br>7           | _ | _ | - | _ | Δ | Δ | Δ | Δ |

| ASLA                | Arithmetic<br>Shift Left A  | C b7 b0                      | A INH                                         | 48                            | _                          | 2                     | _ | _ | _ | _ | Δ | Δ | Δ | Δ |

| ASLB                | Arithmetic<br>Shift Left B  |                              | B INH                                         | 58                            | _                          | 2                     | _ | _ | _ | _ | Δ | Δ | Δ | Δ |

| ASLD                | Arithmetic<br>Shift Left D  |                              | INH                                           | 05                            | _                          | 3                     | _ | _ | _ | _ | Δ | Δ | Δ | Δ |

| ASR                 | Arithmetic<br>Shift Right   | b7 b0 C                      | EXT<br>IND,X<br>IND,Y                         | 77<br>67<br>18 67             | hh II<br>ff<br>ff          | 6<br>6<br>7           | _ | _ | _ | _ | Δ | Δ | Δ | Δ |

| ASRA                | Arithmetic<br>Shift Right A | b7 b0 C                      | A INH                                         | 47                            | _                          | 2                     | _ | _ | _ | _ | Δ | Δ | Δ | Δ |

| ASRB                | Arithmetic<br>Shift Right B | b7 b0 C                      | B INH                                         | 57                            | _                          | 2                     | - | _ | _ | _ | Δ | Δ | Δ | Δ |

| BCC (rel)           | Branch if Carry<br>Clear    | ? C = 0                      | REL                                           | 24                            | rr                         | 3                     | _ | _ | _ | _ | _ | _ | _ | _ |

| BCLR (opr)<br>(msk) | Clear Bit(s)                | $M \cdot (mm) \Rightarrow M$ | DIR<br>IND,X<br>IND,Y                         | 15<br>1D<br>18 1D             | dd mm<br>ff mm<br>ff mm    | 6<br>7<br>8           | _ | _ | _ | _ | Δ | Δ | 0 | _ |

| BCS (rel)           | Branch if Carry<br>Set      | ? C = 1                      | REL                                           | 25                            | rr                         | 3                     | _ | _ | _ | _ | _ | _ | _ | _ |

| BEQ (rel)           | Branch if = Zero            | ? Z = 1                      | REL                                           | 27                            | rr                         | 3                     | _ | _ | _ | _ | _ | _ | _ | _ |

| BGE (rel)           | Branch if ∆<br>Zero         | ? N ⊕ V = 0                  | REL                                           | 2C                            | rr                         | 3                     |   |   |   |   |   | _ |   |   |

Table 3-2 Instruction Set (Sheet 2 of 6)

| Mnemonic                     | Operation                      | Description            | Addressing                                    | Ir                            | struction                        |                       |   |   | Со | nditio | n Co | des |   |   |

|------------------------------|--------------------------------|------------------------|-----------------------------------------------|-------------------------------|----------------------------------|-----------------------|---|---|----|--------|------|-----|---|---|

|                              |                                |                        | Mode                                          | Opcode                        | Operand                          | Cycles                | S | Х | Н  | I      | N    | Z   | ٧ | С |

| BGT (rel)                    | Branch if ><br>Zero            | ? Z + (N ⊕ V) = 0      | REL                                           | 2E                            | rr                               | 3                     | _ | _ | _  | _      | _    | _   | _ | _ |

| BHI (rel)                    | Branch if<br>Higher            | ? C + Z = 0            | REL                                           | 22                            | rr                               | 3                     | _ | _ | _  | _      | _    | _   | _ | _ |

| BHS (rel)                    | Branch if<br>Higher or<br>Same | ? C = 0                | REL                                           | 24                            | rr                               | 3                     | _ |   |    | _      |      | _   | _ | _ |

| BITA (opr)                   | Bit(s) Test A<br>with Memory   | A • M                  | A IMM A DIR A EXT A IND,X A IND,Y             | 85<br>95<br>B5<br>A5<br>18 A5 | ii<br>dd<br>hh II<br>ff          | 2<br>3<br>4<br>4<br>5 | _ | _ | _  | _      | Δ    | Δ   | 0 | _ |

| BITB (opr)                   | Bit(s) Test B<br>with Memory   | B • M                  | B IMM B DIR B EXT B IND,X B IND,Y             | C5<br>D5<br>F5<br>E5<br>18 E5 | ii<br>dd<br>hh II<br>ff          | 2<br>3<br>4<br>4<br>5 | _ | _ | _  | _      | Δ    | Δ   | 0 | _ |

| BLE (rel)                    | Branch if ∆<br>Zero            | ? Z + (N ⊕ V) = 1      | REL                                           | 2F                            | rr                               | 3                     | _ | _ | _  | _      | _    | _   | _ | _ |

| BLO (rel)                    | Branch if<br>Lower             | ? C = 1                | REL                                           | 25                            | rr                               | 3                     | _ | _ | _  | _      | _    | _   | _ | _ |

| BLS (rel)                    | Branch if<br>Lower or<br>Same  | ? C + Z = 1            | REL                                           | 23                            | rr                               | 3                     | _ | _ | _  | _      | _    | _   | _ | _ |

| BLT (rel)                    | Branch if <<br>Zero            | ? N ⊕ V = 1            | REL                                           | 2D                            | rr                               | 3                     | _ | _ | _  | _      | _    | _   | _ | _ |

| BMI (rel)                    | Branch if<br>Minus             | ? N = 1                | REL                                           | 2B                            | rr                               | 3                     | _ |   |    |        | _    |     |   | _ |

| BNE (rel)                    | Branch if not = Zero           | ? Z = 0                | REL                                           | 26                            | rr                               | 3                     | _ | _ | _  | _      | _    | _   | _ | _ |

| BPL (rel)                    | Branch if Plus                 | ? N = 0                | REL                                           | 2A                            | rr                               | 3                     | _ | _ | _  | _      | _    | _   | _ | _ |

| BRA (rel)                    | Branch Always                  | ? 1 = 1                | REL                                           | 20                            | rr                               | 3                     | _ | _ | _  | _      | _    | _   | _ | _ |

| BRCLR(opr)<br>(msk)<br>(rel) | Branch if<br>Bit(s) Clear      | ? M • mm = 0           | DIR<br>IND,X<br>IND,Y                         | 13<br>1F<br>18 1F             | dd mm rr<br>ff mm rr<br>ff mm rr | 6<br>7<br>8           | _ | _ | _  | _      |      | _   | _ | _ |

| BRN (rel)                    | Branch Never                   | ? 1 = 0                | REL                                           | 21                            | rr                               | 3                     | _ | _ | _  | _      | _    | _   | _ | _ |

| BRSET(opr)<br>(msk)<br>(rel) | Branch if Bit(s)<br>Set        | ? (M) • mm = 0         | DIR<br>IND,X<br>IND,Y                         | 12<br>1E<br>18 1E             | dd mm rr<br>ff mm rr<br>ff mm rr | 6<br>7<br>8           | _ | _ | _  | _      | _    | _   | _ | _ |

| BSET (opr)<br>(msk)          | Set Bit(s)                     | $M + mm \Rightarrow M$ | DIR<br>IND,X<br>IND,Y                         | 14<br>1C<br>18 1C             | dd mm<br>ff mm<br>ff mm          | 6<br>7<br>8           | _ | _ | _  | _      | Δ    | Δ   | 0 | _ |

| BSR (rel)                    | Branch to<br>Subroutine        | See Figure 3–2         | REL                                           | 8D                            | rr                               | 6                     | _ | _ | _  | _      | _    | _   | _ | _ |

| BVC (rel)                    | Branch if<br>Overflow Clear    | ? V = 0                | REL                                           | 28                            | rr                               | 3                     | _ | _ | _  | _      | _    | _   | _ | _ |

| BVS (rel)                    | Branch if<br>Overflow Set      | ? V = 1                | REL                                           | 29                            | rr                               | 3                     | _ | _ | _  | _      | _    | _   | _ | _ |

| CBA                          | Compare A to<br>B              | A – B                  | INH                                           | 11                            | _                                | 2                     | _ | _ | _  | _      | Δ    | Δ   | Δ | Δ |

| CLC                          | Clear Carry Bit                | 0 ⇒ C                  | INH                                           | 0C                            | _                                | 2                     | _ | _ | _  | _      | _    | _   | _ | 0 |

| CLI                          | Clear Interrupt<br>Mask        | 0 ⇒ I                  | INH                                           | 0E                            | _                                | 2                     |   | _ | _  | 0      | _    | _   | _ | _ |

| CLR (opr)                    | Clear Memory<br>Byte           | 0 ⇒ M                  | EXT<br>IND,X<br>IND,Y                         | 7F<br>6F<br>18 6F             | hh II<br>ff<br>ff                | 6<br>6<br>7           | _ | _ | _  | _      | 0    | 1   | 0 | 0 |

| CLRA                         | Clear<br>Accumulator A         | 0 ⇒ A                  | A INH                                         | 4F                            | _                                | 2                     | _ | _ | _  | _      | 0    | 1   | 0 | 0 |

| CLRB                         | Clear<br>Accumulator B         | 0 ⇒ B                  | B INH                                         | 5F                            | _                                | 2                     | _ | _ |    | _      | 0    | 1   | 0 | 0 |

| CLV                          | Clear Overflow<br>Flag         | $0 \Rightarrow V$      | INH                                           | 0A                            | _                                | 2                     | _ | _ | _  | _      | _    | _   | 0 | _ |

| CMPA (opr)                   | Compare A to<br>Memory         | A – M                  | A IMM<br>A DIR<br>A EXT<br>A IND,X<br>A IND,Y | 81<br>91<br>B1<br>A1<br>18 A1 | ii<br>dd<br>hh II<br>ff          | 2<br>3<br>4<br>4<br>5 | _ |   |    |        | Δ    | Δ   | Δ | Δ |

| CMPB (opr)                   | Compare B to<br>Memory         | B – M                  | B IMM B DIR B EXT B IND,X B IND,Y             | C1<br>D1<br>F1<br>E1<br>18 E1 | ii<br>dd<br>hh II<br>ff<br>ff    | 2<br>3<br>4<br>4<br>5 | _ | _ | _  |        | Δ    | Δ   | Δ | Δ |

Table 3-2 Instruction Set (Sheet 3 of 6)

| Mnemonic   | Operation                         | Description                              | Addressing                                    | Ir                                        | struction                        |                       |   |   | Со | nditio | n Co | des |   |   |

|------------|-----------------------------------|------------------------------------------|-----------------------------------------------|-------------------------------------------|----------------------------------|-----------------------|---|---|----|--------|------|-----|---|---|

|            |                                   |                                          | Mode                                          | Opcode                                    | Operand                          | Cycles                | S | Х | Н  | ı      | N    | Z   | ٧ | С |

| COM (opr)  | Ones<br>Complement<br>Memory Byte | \$FF – M ⇒ M                             | EXT<br>IND,X<br>IND,Y                         | 73<br>63<br>18 63                         | hh II<br>ff<br>ff                | 6<br>6<br>7           | _ | _ | _  | _      | Δ    | Δ   | 0 | 1 |

| COMA       | Ones<br>Complement<br>A           | \$FF – A ⇒ A                             | A INH                                         | 43                                        | _                                | 2                     | _ | _ | _  | _      | Δ    | Δ   | 0 | 1 |

| COMB       | Ones<br>Complement<br>B           | \$FF – B ⇒ B                             | B INH                                         | 53                                        | _                                | 2                     | _ | _ | _  | _      | Δ    | Δ   | 0 | 1 |

| CPD (opr)  | Compare D to<br>Memory 16-Bit     | D-M:M +1                                 | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y           | 1A 83<br>1A 93<br>1A B3<br>1A A3<br>CD A3 | jj kk<br>dd<br>hh II<br>ff<br>ff | 5<br>6<br>7<br>7<br>7 | _ | _ | _  | _      | Δ    | Δ   | Δ | Δ |

| CPX (opr)  | Compare X to<br>Memory 16-Bit     | IX – M : M + 1                           | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y           | 8C<br>9C<br>BC<br>AC<br>CD AC             | jj kk<br>dd<br>hh II<br>ff<br>ff | 4<br>5<br>6<br>6<br>7 | _ | _ | -  | _      | Δ    | Δ   | Δ | Δ |

| CPY (opr)  | Compare Y to<br>Memory 16-Bit     | IY – M : M + 1                           | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y           | 18 8C<br>18 9C<br>18 BC<br>1A AC<br>18 AC | jj kk<br>dd<br>hh II<br>ff<br>ff | 5<br>6<br>7<br>7<br>7 | _ | _ | _  | _      | Δ    | Δ   | Δ | Δ |

| DAA        | Decimal Adjust<br>A               | Adjust Sum to BCD                        | INH                                           | 19                                        | _                                | 2                     | _ | _ | _  | _      | Δ    | Δ   | Δ | Δ |

| DEC (opr)  | Decrement<br>Memory Byte          | M − 1 ⇒ M                                | EXT<br>IND,X<br>IND,Y                         | 7A<br>6A<br>18 6A                         | hh II<br>ff<br>ff                | 6<br>6<br>7           | _ | _ | _  | _      | Δ    | Δ   | Δ | _ |

| DECA       | Decrement<br>Accumulator<br>A     | $A-1 \Rightarrow A$                      | A INH                                         | 4A                                        | _                                | 2                     | _ | _ | _  | _      | Δ    | Δ   | Δ | _ |

| DECB       | Decrement<br>Accumulator<br>B     | B – 1 ⇒ B                                | B INH                                         | 5A                                        | _                                | 2                     | _ |   | _  | _      | Δ    | Δ   | Δ | _ |

| DES        | Decrement<br>Stack Pointer        | SP – 1 ⇒ SP                              | INH                                           | 34                                        | _                                | 3                     | _ | _ | _  | _      | _    | _   | _ |   |

| DEX        | Decrement<br>Index Register<br>X  | $IX - 1 \Rightarrow IX$                  | INH                                           | 09                                        | _                                | 3                     | _ | _ | _  | _      | _    | Δ   | _ | _ |

| DEY        | Decrement<br>Index Register<br>Y  | IY − 1 ⇒ IY                              | INH                                           | 18 09                                     | _                                | 4                     | _ | _ | _  | _      | _    | Δ   | _ | _ |

| EORA (opr) | Exclusive OR<br>A with Memory     | $A \oplus M \Rightarrow A$               | A IMM<br>A DIR<br>A EXT<br>A IND,X<br>A IND,Y | 88<br>98<br>B8<br>A8<br>18 A8             | ii<br>dd<br>hh II<br>ff          | 2<br>3<br>4<br>4<br>5 | _ | _ | _  | _      | Δ    | Δ   | 0 |   |

| EORB (opr) | Exclusive OR<br>B with Memory     | $B \oplus M \Rightarrow B$               | B IMM B DIR B EXT B IND,X B IND,Y             | C8<br>D8<br>F8<br>E8                      | ii<br>dd<br>hh II<br>ff          | 2<br>3<br>4<br>4<br>5 | _ | _ | _  | _      | Δ    | Δ   | 0 | _ |

| FDIV       | Fractional<br>Divide 16 by<br>16  | $D/IX \Rightarrow IX; r \Rightarrow D$   | INH                                           | 03                                        | _                                | 41                    | _ | _ | _  | _      | _    | Δ   | Δ | Δ |

| IDIV       | Integer Divide<br>16 by 16        | $D / IX \Rightarrow IX; r \Rightarrow D$ | INH                                           | 02                                        | _                                | 41                    | _ | _ | _  | _      | _    | Δ   | 0 | Δ |

| INC (opr)  | Increment<br>Memory Byte          | M + 1 ⇒ M                                | EXT<br>IND,X<br>IND,Y                         | 7C<br>6C<br>18 6C                         | hh II<br>ff<br>ff                | 6<br>6<br>7           | _ | _ | _  | _      | Δ    | Δ   | Δ | _ |

| INCA       | Increment<br>Accumulator<br>A     | A + 1 ⇒ A                                | A INH                                         | 4C                                        |                                  | 2                     | _ | - | _  | _      | Δ    | Δ   | Δ |   |

| INCB       | Increment<br>Accumulator<br>B     | B + 1 ⇒ B                                | B INH                                         | 5C                                        | _                                | 2                     | _ | _ | _  | _      | Δ    | Δ   | Δ |   |

| INS        | Increment<br>Stack Pointer        | SP + 1 ⇒ SP                              | INH                                           | 31                                        | _                                | 3                     | _ | _ | _  | _      | _    | _   | _ | _ |

| INX        | Increment<br>Index Register<br>X  | IX + 1 ⇒ IX                              | INH                                           | 08                                        | _                                | 3                     | _ | _ | _  | _      | _    | Δ   | _ | _ |

Table 3-2 Instruction Set (Sheet 4 of 6)

| Mnemonic         | Operation                                    | Description                                 | Addressing                                    |                      |                            | struction                        |                       |   |   |   | nditio |   |   |   |                   |

|------------------|----------------------------------------------|---------------------------------------------|-----------------------------------------------|----------------------|----------------------------|----------------------------------|-----------------------|---|---|---|--------|---|---|---|-------------------|

|                  |                                              |                                             | Mode                                          | Opcod                |                            | Operand                          | Cycles                | S | Х | Н | ı      | N | Z | ٧ | С                 |

| INY              | Increment<br>Index Register<br>Y             | IY + 1 ⇒ IY                                 | INH                                           | 18                   | 80                         | _                                | 4                     | _ | _ | _ | _      | _ | Δ | _ | _                 |

| JMP (opr)        | Jump                                         | See Figure 3–2                              | EXT<br>IND,X<br>IND,Y                         |                      | 7E<br>6E<br>6E             | hh II<br>ff<br>ff                | 3<br>3<br>4           | _ | _ | _ | _      |   | _ | _ | _                 |

| JSR (opr)        | Jump to<br>Subroutine                        | See Figure 3–2                              | DIR<br>EXT<br>IND,X<br>IND,Y                  |                      | 9D<br>BD<br>AD<br>AD       | dd<br>hh II<br>ff<br>ff          | 5<br>6<br>6<br>7      | _ | _ | _ | _      | _ | _ | _ | _                 |

| LDAA (opr)       | Load<br>Accumulator<br>A                     | $M \Rightarrow A$                           | A IMM<br>A DIR<br>A EXT<br>A IND,X<br>A IND,Y |                      | 86<br>96<br>B6<br>A6<br>A6 | ii<br>dd<br>hh II<br>ff<br>ff    | 2<br>3<br>4<br>4<br>5 |   |   | _ | _      | Δ | Δ | 0 |                   |

| LDAB (opr)       | Load<br>Accumulator<br>B                     | $M \Rightarrow B$                           | B IMM B DIR B EXT B IND,X B IND,Y             |                      | C6<br>D6<br>F6<br>E6       | ii<br>dd<br>hh II<br>ff          | 2<br>3<br>4<br>4<br>5 |   | _ |   | _      | Δ | Δ | 0 |                   |

| LDD (opr)        | Load Double<br>Accumulator<br>D              | $M \Rightarrow A, M + 1 \Rightarrow B$      | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y           |                      | CC<br>DC<br>FC<br>EC       | jj kk<br>dd<br>hh II<br>ff       | 3<br>4<br>5<br>5      | _ | _ | _ | _      | Δ | Δ | 0 | _                 |

| LDS (opr)        | Load Stack<br>Pointer                        | M:M+1⇒SP                                    | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y           |                      | 8E<br>9E                   | jj kk<br>dd<br>hh II<br>ff<br>ff | 3<br>4<br>5<br>5      | _ | _ | _ | _      | Δ | Δ | 0 | _                 |

| LDX (opr)        | Load Index<br>Register<br>X                  | M : M + 1 ⇒ IX                              | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y           |                      | CE<br>DE<br>FE<br>EE       | jj kk<br>dd<br>hh II<br>ff<br>ff | 3<br>4<br>5<br>5<br>6 | _ | _ | _ | _      | Δ | Δ | 0 | _                 |

| LDY (opr)        | Load Index<br>Register<br>Y                  | M : M + 1 ⇒ IY                              | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y           | 18<br>18<br>18<br>1A | CE<br>DE<br>FE<br>EE       | jj kk<br>dd<br>hh II<br>ff<br>ff | 4<br>5<br>6<br>6      |   | _ |   |        | Δ | Δ | 0 |                   |

| LSL (opr)        | Logical Shift<br>Left                        |                                             | EXT<br>IND,X<br>IND,Y                         |                      | 78<br>68<br>68             | hh II<br>ff<br>ff                | 6<br>6<br>7           |   | - | _ | _      | Δ | Δ | Δ | Δ                 |

| LSLA             | Logical Shift<br>Left A                      |                                             | A INH                                         |                      | 48                         | <del>-</del>                     | 2                     |   | _ | _ | _      | Δ | Δ | Δ | Δ                 |

| LSLB             | Logical Shift<br>Left B                      |                                             | B INH                                         |                      | 58                         | _                                | 2                     | _ | _ | _ | _      | Δ | Δ | Δ | Δ                 |

| LSLD             | Logical Shift<br>Left Double                 | C b7 A b0 b7 B b0                           | INH                                           |                      | 05                         | _                                | 3                     | _ | _ | _ | _      | Δ | Δ | Δ | Δ                 |

| LSR (opr)        | Logical Shift<br>Right                       | 0                                           | EXT<br>IND,X<br>IND,Y                         |                      | 74<br>64<br>64             | hh II<br>ff<br>ff                | 6<br>6<br>7           |   | _ | _ | _      | 0 | Δ | Δ | Δ                 |

| LSRA             | Logical Shift<br>Right A                     | 0                                           | A INH                                         |                      | 44                         | _                                | 2                     | _ | _ | _ | _      | 0 | Δ | Δ | Δ                 |

| LSRB             | Logical Shift<br>Right B                     | 0                                           | B INH                                         |                      | 54                         | _                                | 2                     | _ | _ | _ | _      | 0 | Δ | Δ | Δ                 |

| LSRD             | Logical Shift<br>Right Double                | 0+0+0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0     | INH                                           |                      | 04                         | _                                | 3                     | _ | _ | _ | _      | 0 | Δ | Δ | Δ                 |

| MUL<br>NEG (opr) | Multiply 8 by 8 Two's Complement Memory Byte | $A * B \Rightarrow D$ $0 - M \Rightarrow M$ | INH<br>EXT<br>IND,X<br>IND,Y                  |                      | 3D<br>70<br>60<br>60       | hh II<br>ff<br>ff                | 10<br>6<br>6<br>7     | _ | _ | _ | _      | Δ | Δ | Δ | $\Delta$ $\Delta$ |

| NEGA             | Two's<br>Complement<br>A                     | 0 − A ⇒ A                                   | A INH                                         |                      | 40                         | _                                | 2                     | _ | _ | _ | _      | Δ | Δ | Δ | Δ                 |

| NEGB             | Two's<br>Complement<br>B                     | 0 − B ⇒ B                                   | B INH                                         |                      | 50                         | _                                | 2                     | _ | _ | _ | _      | Δ | Δ | Δ | Δ                 |

Table 3-2 Instruction Set (Sheet 5 of 6)

| Mnemonic   | Operation                          | Description                      | Addressing |                |          |         | ruction     | 1 -    |   |          |   | nditio   |          |          |          |          |

|------------|------------------------------------|----------------------------------|------------|----------------|----------|---------|-------------|--------|---|----------|---|----------|----------|----------|----------|----------|

|            |                                    |                                  |            | Mode           | Opcode   | (       | Operand     | Cycles | S | Х        | Н | I        | N        | Z        | ٧        | С        |

| NOP        | No operation                       | No Operation                     |            | INH            | 01       |         |             | 2      |   | _        | _ | _        | _        | _        | _        | _        |

| ORAA (opr) | OR                                 | $A + M \Rightarrow A$            | A          | IMM            | 8A       |         |             | 2      | _ | _        | _ | _        | $\Delta$ | $\Delta$ | 0        | _        |

|            | Accumulator<br>A (Inclusive)       |                                  | A          | DIR<br>EXT     | 9A<br>B/ |         | ld<br>ih II | 3<br>4 |   |          |   |          |          |          |          |          |

|            | A (IIIClusive)                     |                                  | A          | IND,X          | AA       |         |             | 4      |   |          |   |          |          |          |          |          |

|            |                                    |                                  | A          | IND,Y          | 18 AA    |         |             | 5      |   |          |   |          |          |          |          |          |

| ORAB (opr) | OR                                 | $B + M \Rightarrow B$            | В          | IMM            | CA       |         |             | 2      |   |          |   |          | Δ        | Δ        | 0        |          |

|            | Accumulator                        | · _                              | В          | DIR            | DA       |         | ld          | 3      |   |          |   |          | _        |          |          |          |

|            | B (Inclusive)                      |                                  | В          | EXT            | FA       |         | ıh II       | 4      |   |          |   |          |          |          |          |          |

|            |                                    |                                  | В          | IND,X          | EA       |         |             | 4      |   |          |   |          |          |          |          |          |

|            |                                    |                                  | В          | IND,Y          | 18 EA    |         | f           | 5      |   |          |   |          |          |          |          |          |

| PSHA       | Push A onto<br>Stack               | $A \Rightarrow Stk,SP = SP - 1$  | A          | INH            | 36       |         | _           | 3      | — | _        | _ | _        | _        | _        | _        | _        |

| PSHB       | Push B onto<br>Stack               | $B \Rightarrow Stk,SP = SP - 1$  | В          | INH            | 37       |         | _           | 3      | _ | _        | _ | _        | _        | _        | _        | _        |

| PSHX       | Push X onto                        | $IX \Rightarrow Stk,SP = SP - 2$ |            | INH            | 3C       | :       |             | 4      | _ |          |   |          | _        |          |          |          |

|            | Stack (Lo<br>First)                | ,                                |            |                |          |         |             |        |   |          |   |          |          |          |          |          |

| PSHY       | Push Y onto                        | IY⇒Stk,SP=SP-2                   |            | INH            | 18 3C    | +       |             | 5      |   |          |   |          |          |          |          |          |

| 13111      | Stack (Lo<br>First)                | 77 → 3tk,3F = 3F = 2             |            | IINII          | 10 30    |         |             | 3      | _ |          |   |          |          |          |          |          |

| PULA       | Pull A from                        | SP = SP + 1, A ← Stk             | A          | INH            | 32       |         | _           | 4      | _ | _        | _ | _        | _        | _        | _        | _        |

| DI II D    | Stack                              | OD = OD : 4 D                    | <u> </u>   | INTER          | 0.0      | $\perp$ |             | 4      |   |          |   |          |          |          |          |          |

| PULB       | Pull B from<br>Stack               | $SP = SP + 1, B \leftarrow Stk$  | В          | INH            | 33       |         | _           | 4      | _ | _        | _ | _        | _        | _        | _        | _        |

| PULX       | Pull X From<br>Stack (Hi<br>First) | SP = SP + 2, IX ←<br>Stk         |            | INH            | 38       |         | _           | 5      | _ | _        | _ | _        | _        | _        | _        | _        |

| PULY       | Pull Y from<br>Stack (Hi<br>First) | SP = SP + 2, IY ←<br>Stk         |            | INH            | 18 38    |         | _           | 6      | _ | _        | _ | _        | -        | _        | _        | _        |

| POL (apr)  | Rotate Left                        |                                  |            | EXT            | 79       | h       | ıh II       | 6      |   |          |   |          | Δ        | Δ        | Δ        | Δ        |

| ROL (opr)  | Rotate Left                        |                                  |            | IND,X          | 69       |         |             | 6      | _ |          |   | _        | Δ        | Δ        | Δ        | Δ        |

|            |                                    | C b7 b0                          |            | IND,X<br>IND,Y | 18 69    |         |             | 7      |   |          |   |          |          |          |          |          |

| ROLA       | Rotate Left A                      | C 07 00                          | Α          | INH            | 49       |         | _           | 2      |   |          |   |          | Δ        | Δ        | Δ        | Δ        |

| NOLA       | Notate Left A                      | C b7 b0                          |            | IINII          | 49       |         |             | 2      | _ |          |   |          | Δ        | Δ        | Δ        | Δ        |

| ROLB       | Rotate Left B                      | C b/ b0                          | В          | INH            | 59       | _       |             | 2      |   |          |   |          | Δ        | Δ        | Δ        | Δ        |

| NOLD       | Notate Left B                      | C b7 b0                          |            | IINII          | 39       |         |             |        |   |          |   |          | Δ        | Δ        | Δ        | Δ        |

| ROR (opr)  | Rotate Right                       | C b/ b0                          |            | EXT            | 76       | h       | ıh II       | 6      |   |          |   |          | Δ        | Δ        | Δ        | Δ        |

| NON (opi)  | Totale High                        |                                  |            | IND,X          | 66       |         |             | 6      |   |          |   |          | Δ        | Δ        | Δ        | Δ        |

|            |                                    | b7 b0 C                          |            | IND,Y          | 18 66    |         |             | 7      |   |          |   |          |          |          |          |          |

| RORA       | Rotate Right A                     | t .                              | Α          | INH            | 46       |         | _           | 2      |   |          |   |          | Δ        | Δ        | Δ        | Δ        |

| ROINA      | Ttotate ragilit A                  |                                  | ^          | 11411          | 40       |         |             | _      |   |          |   |          |          |          |          |          |

|            |                                    | b7 b0 C                          |            |                |          |         |             |        |   |          |   |          |          |          |          |          |

| RORB       | Rotate Right B                     |                                  | В          | INH            | 56       |         | _           | 2      | _ |          |   |          | Δ        | Δ        | Δ        | Δ        |

|            |                                    | ·                                |            |                |          |         |             |        |   |          |   |          |          |          |          |          |

|            |                                    | b7 b0 C                          |            |                |          |         |             |        |   |          |   |          |          |          |          |          |

| RTI        | Return from                        | See Figure 3–2                   |            | INH            | 3B       |         | _           | 12     | Δ | <b>\</b> | Δ | $\Delta$ | Δ        | Δ        | Δ        | Δ        |

|            | Interrupt                          |                                  |            |                |          |         |             | _      |   |          |   |          |          |          |          |          |

| RTS        | Return from<br>Subroutine          | See Figure 3–2                   |            | INH            | 39       |         | _           | 5      | _ | _        | _ | _        | _        | _        | _        | _        |

| SBA        | Subtract B<br>from A               | $A - B \Rightarrow A$            |            | INH            | 10       |         | _           | 2      | _ | _        | _ | _        | Δ        | Δ        | Δ        | Δ        |

| SBCA (opr) | Subtract with                      | $A - M - C \Rightarrow A$        | Α          | IMM            | 82       | ii      |             | 2      | _ | _        | _ | _        | Δ        | Δ        | Δ        | Δ        |

| /          | Carry from A                       |                                  | Α          | DIR            | 92       | d       | ld          | 3      |   |          |   |          |          |          |          |          |

|            |                                    |                                  | Α          | EXT            | B2       | 2 h     | ıh II       | 4      |   |          |   |          |          |          |          |          |

|            |                                    |                                  | Α          | IND,X          | A2       |         |             | 4      |   |          |   |          |          |          |          |          |

|            |                                    |                                  | Α          | IND,Y          | 18 A2    |         |             | 5      |   |          |   |          |          |          |          |          |

| SBCB (opr) | Subtract with                      | $B - M - C \Rightarrow B$        | В          | IMM            | C2       |         |             | 2      | — | _        | _ |          | Δ        | $\Delta$ | $\Delta$ | $\Delta$ |

|            | Carry from B                       |                                  | B<br>B     | DIR<br>EXT     | D2<br>F2 |         | ld<br>ih II | 3<br>4 |   |          |   |          |          |          |          |          |

|            |                                    |                                  | В          | IND,X          | E2       |         |             | 4      |   |          |   |          |          |          |          |          |

|            |                                    |                                  | В          | IND,X          | 18 E2    |         |             | 5      |   |          |   |          |          |          |          |          |

| SEC        | Set Carry                          | 1 ⇒ C                            |            | INH            | 0D       |         | _           | 2      | _ | _        |   |          | -        |          |          | 1        |

| SEI        | Set Interrupt                      | 1 ⇒ l                            |            | INH            | 0F       |         |             | 2      |   | _        |   | 1        |          |          |          |          |

|            | Mask                               |                                  |            |                |          |         |             |        |   |          |   |          |          |          |          |          |

| SEV        | Set Overflow<br>Flag               | 1 ⇒ V                            |            | INH            | 0B       |         | _           | 2      | - | _        | _ | _        | -        | _        | 1        | _        |

| STAA (opr) | Store                              | $A \Rightarrow M$                | Α          | DIR            | 97       |         | ld          | 3      | _ | _        | _ | _        | Δ        | Δ        | 0        | _        |

|            | Accumulator                        |                                  | Α          | EXT            | B7       |         | ıh II       | 4      |   |          |   |          |          |          |          |          |

|            | A                                  |                                  | A          | IND,X          | A7       | 7 ff    | 1           | 4      |   |          |   |          |          |          |          |          |

|            | 1                                  | l .                              | Α          | IND,Y          | 18 A7    | 7  ff   | Ī           | 5      | l |          |   |          | 1        |          |          |          |

Table 3-2 Instruction Set (Sheet 6 of 6)

| Mnemonic   | Operation                         | Ad                                     | ldressing        |                                     | In                   | struction                  |                               |                       |   | Co       | nditio | n Co | des |   |   |   |

|------------|-----------------------------------|----------------------------------------|------------------|-------------------------------------|----------------------|----------------------------|-------------------------------|-----------------------|---|----------|--------|------|-----|---|---|---|

|            |                                   |                                        |                  | Mode                                | Or                   | code                       | Operand                       | Cycles                | S | Х        | Н      | I    | N   | Z | V | С |

| STAB (opr) | Store<br>Accumulator<br>B         | $B \Rightarrow M$                      | В<br>В<br>В<br>В | DIR<br>EXT<br>IND,X<br>IND,Y        | 18                   | D7<br>F7<br>E7<br>E7       | dd<br>hh II<br>ff<br>ff       | 3<br>4<br>4<br>5      | _ | _        | _      | _    | Δ   | Δ | 0 | _ |

| STD (opr)  | Store<br>Accumulator<br>D         | $A \Rightarrow M, B \Rightarrow M + 1$ |                  | DIR<br>EXT<br>IND,X<br>IND,Y        | 18                   | DD<br>FD<br>ED<br>ED       |                               | 4<br>5<br>5<br>6      | _ |          |        |      | Δ   | Δ | 0 | _ |

| STOP       | Stop Internal<br>Clocks           | _                                      |                  | INH                                 |                      | CF                         | _                             | 2                     | _ | _        | _      | _    | -   | _ | _ | _ |

| STS (opr)  | Store Stack<br>Pointer            | SP ⇒ M : M + 1                         |                  | DIR<br>EXT<br>IND,X<br>IND,Y        | 18                   | 9F<br>BF<br>AF<br>AF       | dd<br>hh II<br>ff<br>ff       | 4<br>5<br>5<br>6      | _ | _        | _      | _    | Δ   | Δ | 0 | _ |

| STX (opr)  | Store Index<br>Register X         | IX ⇒ M : M + 1                         |                  | DIR<br>EXT<br>IND,X<br>IND,Y        | CD                   | DF<br>FF<br>EF<br>EF       | dd<br>hh II<br>ff             | 4<br>5<br>5<br>6      | _ |          |        |      | Δ   | Δ | 0 | _ |

| STY (opr)  | Store Index<br>Register Y         | IY ⇒ M : M + 1                         |                  | DIR<br>EXT<br>IND,X<br>IND,Y        | 18<br>18<br>1A<br>18 | DF<br>FF<br>EF<br>EF       | dd<br>hh II<br>ff<br>ff       | 5<br>6<br>6           | _ | _        | _      | _    | Δ   | Δ | 0 | _ |

| SUBA (opr) | Subtract<br>Memory from<br>A      | $A-M\RightarrowA$                      | A<br>A<br>A<br>A | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18                   | 80<br>90<br>B0<br>A0<br>A0 | ii<br>dd<br>hh II<br>ff<br>ff | 2<br>3<br>4<br>4<br>5 |   | _        | _      |      | Δ   | Δ | Δ | Δ |

| SUBB (opr) | Subtract<br>Memory from<br>B      | $B-M\RightarrowB$                      | A<br>A<br>A<br>A | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18                   | C0<br>D0<br>F0<br>E0<br>E0 | ii<br>dd<br>hh II<br>ff       | 2<br>3<br>4<br>4<br>5 | _ | _        | _      | _    | Δ   | Δ | Δ | Δ |

| SUBD (opr) | Subtract<br>Memory from<br>D      | D − M : M + 1 ⇒ D                      |                  | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18                   | 83<br>93<br>B3<br>A3<br>A3 | jj kk<br>dd<br>hh II<br>ff    | 4<br>5<br>6<br>6<br>7 | _ | _        | _      | _    | Δ   | Δ | Δ | Δ |

| SWI        | Software<br>Interrupt             | See Figure 3–2                         |                  | INH                                 |                      | 3F                         | _                             | 14                    | _ | _        | _      | 1    | -   | _ | _ | _ |

| TAB        | Transfer A to B                   | $A \Rightarrow B$                      |                  | INH                                 |                      | 16                         | _                             | 2                     | _ | _        | _      | _    | Δ   | Δ | 0 | _ |

| TAP        | Transfer A to CC Register         | A ⇒ CCR                                |                  | INH                                 |                      | 06                         |                               | 2                     | Δ | <b>\</b> | Δ      | Δ    | Δ   | Δ | Δ | Δ |

| TBA        | Transfer B to A                   | $B \Rightarrow A$                      |                  | INH                                 |                      | 17                         | _                             | 2                     |   | _        | _      | _    | Δ   | Δ | 0 | _ |

| TEST       | TEST (Only in<br>Test Modes)      | Address Bus Counts                     |                  | INH                                 |                      | 00                         | _                             | *                     |   | _        |        | _    | _   | _ | _ | _ |

| TPA        | Transfer CC<br>Register to A      | CCR ⇒ A                                |                  | INH                                 |                      | 07                         | _                             | 2                     | _ | _        | _      | _    | _   | _ | _ | _ |

| TST (opr)  | Test for Zero<br>or Minus         | M – 0                                  |                  | EXT<br>IND,X<br>IND,Y               | 18                   | 7D<br>6D<br>6D             | hh II<br>ff<br>ff             | 6<br>6<br>7           | _ | _        | _      | _    | Δ   | Δ | 0 | 0 |

| TSTA       | Test A for Zero<br>or Minus       | A – 0                                  | А                | INH                                 |                      | 4D                         | _                             | 2                     | _ |          | _      | _    | Δ   | Δ | 0 | 0 |

| TSTB       | Test B for Zero<br>or Minus       | B – 0                                  | В                | INH                                 |                      | 5D                         | _                             | 2                     | - | _        | _      | _    | Δ   | Δ | 0 | 0 |

| TSX        | Transfer<br>Stack Pointer<br>to X | SP + 1 ⇒ IX                            |                  | INH                                 |                      | 30                         | _                             | 3                     | _ | _        | _      | _    | _   | _ | _ | _ |

| TSY        | Transfer<br>Stack Pointer<br>to Y | SP + 1 ⇒ IY                            |                  | INH                                 | 18                   | 30                         | _                             | 4                     | _ | _        | _      | _    | _   | _ | _ | _ |

| TXS        | Transfer X to<br>Stack Pointer    | IX – 1 ⇒ SP                            |                  | INH                                 |                      | 35                         | _                             | 3                     | _ | _        | _      | _    | _   | _ | _ | _ |

| TYS        | Transfer Y to<br>Stack Pointer    | IY – 1 ⇒ SP                            |                  | INH                                 | 18                   | 35                         | _                             | 4                     | _ | _        | _      | _    | -   | _ | _ | _ |

| WAI        | Wait for<br>Interrupt             | Stack Regs & WAIT                      |                  | INH                                 |                      | 3E                         | _                             | **                    | _ | _        | _      | _    | -   | _ | _ | _ |

| XGDX       | Exchange D<br>with X              | $IX \Rightarrow D, D \Rightarrow IX$   |                  | INH                                 |                      | 8F                         | _                             | 3                     | _ | _        | _      | _    | -   | _ | _ | _ |

| XGDY       | Exchange D<br>with Y              | $IY \Rightarrow D, D \Rightarrow IY$   |                  | INH                                 | 18                   | 8F                         | _                             | 4                     | - | _        | -      | _    | -   | _ | _ | _ |

# VII) Editeur assembleur:

## A) Fenêtre de l'éditeur :

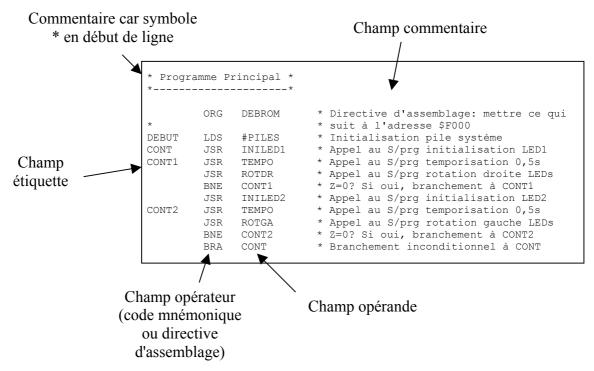

On remarque que l'écran se découpe en 4 champs :

- ♦ Champ étiquette

- \$\text{Champ opérateur (code mnémonique) ou directive d'assemblage}

- \$\text{Champ opérande}\$

- ♦ Champ commentaire

Pour passer d'un champ à un autre, il suffit de mettre un espace avec la touche espace ou TAB. Plusieurs espaces accolés correspond à un seul et même espace. Attention on ne peut sauter des champs, c'est à dire passer du champ étiquette au champ opérande. Seul le champ commentaire est un peu particulier. Si un champ quelconque est rempli, on peut aller directement au champ commentaire. Il y a une exception, lorsqu'aucun champ n'est rempli, l'éditeur considère que toute la ligne est un champ commentaire, d'où la condition de mettre \* en début de ligne.

On n'utilisera pas d'étiquette comportant plus de 8 caractères du code ASCII standard.

# B) <u>Directives d'assemblage</u>:

**END** Fin du fichier contenant le programme.

**EQU** Permet de donner des équivalences.

Ex: PORTB EQU \$1004.

**ORG** Détermine où le compilateur doît mettre les codes qui suivent cette commande.

Ex: ORG \$1000.

**RMB** Réserve une quantité de mémoire (octet).

Ex: RMB 8

**FCB** Permet de mettre des valeurs d'octets fixes dans des zones mémoire.

**FCD** Permet de mettre des valeurs de mots de 16 bits dans des zones mémoire

FCC Permet de mettre des caractères de la table ASCII dans des zones mémoire

<u>Remarque</u>: FCB, FCD, FCC et RMB s'utilisent avec la commande ORG afin de spécifier

les zones mémoires affectées.